Тема 3. Версії мікроконтролерів, оснащені ПЗП з ультрафіолетовим стиранням

| Сайт: | Навчально-інформаційний портал НУБіП України |

| Курс: | Програмне забезпечення вбудованих систем (ІПЗ) |

| Книга: | Тема 3. Версії мікроконтролерів, оснащені ПЗП з ультрафіолетовим стиранням |

| Надруковано: | Гість-користувач |

| Дата: | четвер, 2 квітня 2026, 21:09 |

Опис

Формування компетенцій

ЗК 3, ФК 2, ФК 7, ФК 10, ФК 12.

Програмування мікроконтролера з УФ-ПЗП. Захист від зовнішнього читання УФ-ПЗП в МК x51. Реакція УФ-ПЗП на світло.

Зміст

- 1. Версії мікроконтролерів, оснащені ПЗП з ультрафіолетовим стиранням

- 2. Вбудовані системи керування (ВСК)

- 3. Багаторівнева система керування

- 4. Контрольні питання

- 5. Пам’ять та регістри загального призначення ( на прикладі запам'ятовувального пристрою МК х51)

- 6. Відладчики роботи МК

- 7. Цикл виконання команди ( на прикладі запам'ятовувального пристрою МК х51)

1. Версії мікроконтролерів, оснащені ПЗП з ультрафіолетовим стиранням

Мікросхема 8051 і її вітчизняний аналог 1816ВЕ51 оснащені ма- сочно програмованим внутрішнім ПЗП, що передбачає однократне програмування на заводі-виготовлювачі. Самостійно програмувати такі варіанти мікроконтролерів можна лише за наявності зовнішнього ПЗП.

Версії мікроконтролерів, оснащені ПЗП з ультрафіолетовим стиранням (УФ-ПЗП) можуть бути багато разів перепрограмовані, що значно підвищує зручність використання при розробці нестандартних програм. Від Intel - це версії 8751 (N-МОП) і 87C51 (ДО-МОН). Радянська мікросхема 1816BE751 (аналог 8751) на практиці не зустрічається.

Програмування мікроконтролера з УФ-ПЗП

Процедура програмування мікроконтролера з УФ-ПЗП декілька розрізняється залежно від базової технології його виробництва:

- n-МОП - при напрузі ипрг на вході EA /Vpp (ніжка 31) від 21 до 25 В; запис кожного байта - одним імпульсом 50- мілісекунди; загальний час програмування - 4 мин.

- k-МОН - ипрг = 12,75 В; запис кожного байта - послідовністю з 25 100-микросекундных імпульсів; загальний час програмування - близько 13 секунд.

Підключення мікроконтролера N-МОП до програматора показано на рисунку 32:

Мікроконтролер повинен працювати на зниженій частоті 4,6 МГц із-за необхідності мультиплексування на внутрішній шині адресної і кодової інформації.

Як видно на рисунку, адреси подаються на виводи P1-P2, а коди команд (завантажувані байти) - на P0. Виводи P2.4-6 і PSEN мають бути заземлені. На P2.7 і RST подається логічна «1». На EA / Vpp підтримується рівень +5 В. В момент завантаження байта EA / Vpp підключається до джерела U = +21 В, при цьому на ALE повинен утримуватися 0 протягом як мінімум 50 мс (потім - знову +5 В). Джерело +21 В має бути добре стабілізоване (зниження ипрг може привести до збою програмування, а перевищення більш, ніж на 1 В - до пошкодження мікросхеми).

Захист від зовнішнього читання УФ-ПЗП в МК x51

Розробниками з Intel для мікроконтролерів з УФ-ПЗП передбачений так званий біт захисту, що перешкоджає (при 1) доступ на читання до внутрішнього ПЗП ззовні.

При цьому пристрій і його програма виявляються захищені від несанкціонованого копіювання.

Запис біта захисту здійснюється подібно до запису програми, за виключенням:

• на P2.6 необхідно подати «1»;

• значення на Р0, Р1 і Р2.0-3 можуть бути довільними.

Очищення біта захисту (штатним чином) здійснюється шляхом повного стирання вмісту УФ-ПЗП.

У новіших версіях мікроконтролерах система захисту була ускладнена з метою перешкодити вибірковому стиранню біта захисту вузьконаправленим ультрафіолетовим випромінювачем.

Якщо біт захисту дорівнює 0, вміст УФ-ПЗП може бути прочитаний з метою перевірки правильності (верифікації) завантаження програми.

Читання УФ-ПЗП може здійснюватися за допомогою програма- тора. Адреса подається як і при записі. На Р2.7 необхідно подавати «0» в якості строб-сигнала читання.

Реакція УФ-ПЗП на світло

Вікно мікроконтролера необхідно закривати непрозорою наклейкою. Це необхідно для захисту не лише ПЗП, але і інших внутрішніх елементів (у тому числі ОЗП), які можуть почати збої внаслідок іонізації кремнію при попаданні світла на кристал або кремнієву підкладку.

Стирання УФ-ПЗП здійснюється джерелом УФ-випромінювача з довжиною хвилі < 400 нм. При потужності 12 мВт/см2 кварцевої лампи і відстані до вікна мікроконтролера 1.2 см достатньо 10-15 хвилин для надійного стирання інформації. Дуже тривале опромінення (> 20 хвилин) може вивести мікросхему з ладу.

У спектрі сонячного і люмінесцентного світла присутнє випромінювання з довжиною хвилі < 400 нм. Перебування відкритої мікросхеми на сонячному світлу більше тижня або під люмінесцентними лампами більше 3 років може привести до спотворення вмісту УФ-ПЗП.

2. Вбудовані системи керування (ВСК)

Залежно від складності завдання, вбудовані системи керування можуть бути:

Нижній рівень – багаторівневої СК вирішує завдання безпосереднього керування окремими компонентами устаткування, а верхній рівень – завдання:

З погляду виробників мікропроцесорної техніки всі завдання,кі розв'язуються вбудованими системами, поділяються на два великих класи:

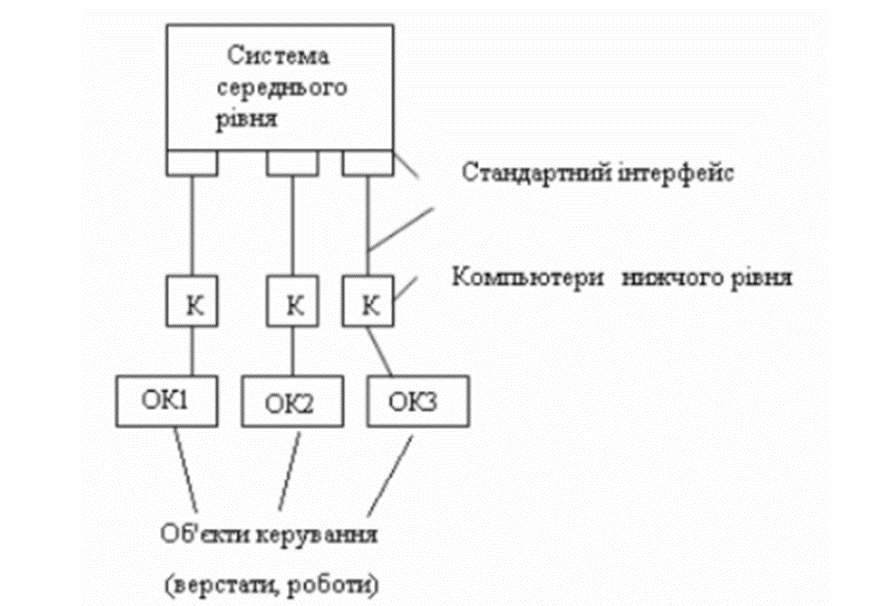

3. Багаторівнева система керування

Багаторівнева

система керування

Підключення комп'ютерів нижнього рівня до системи середнього рівня може здійснюватися:

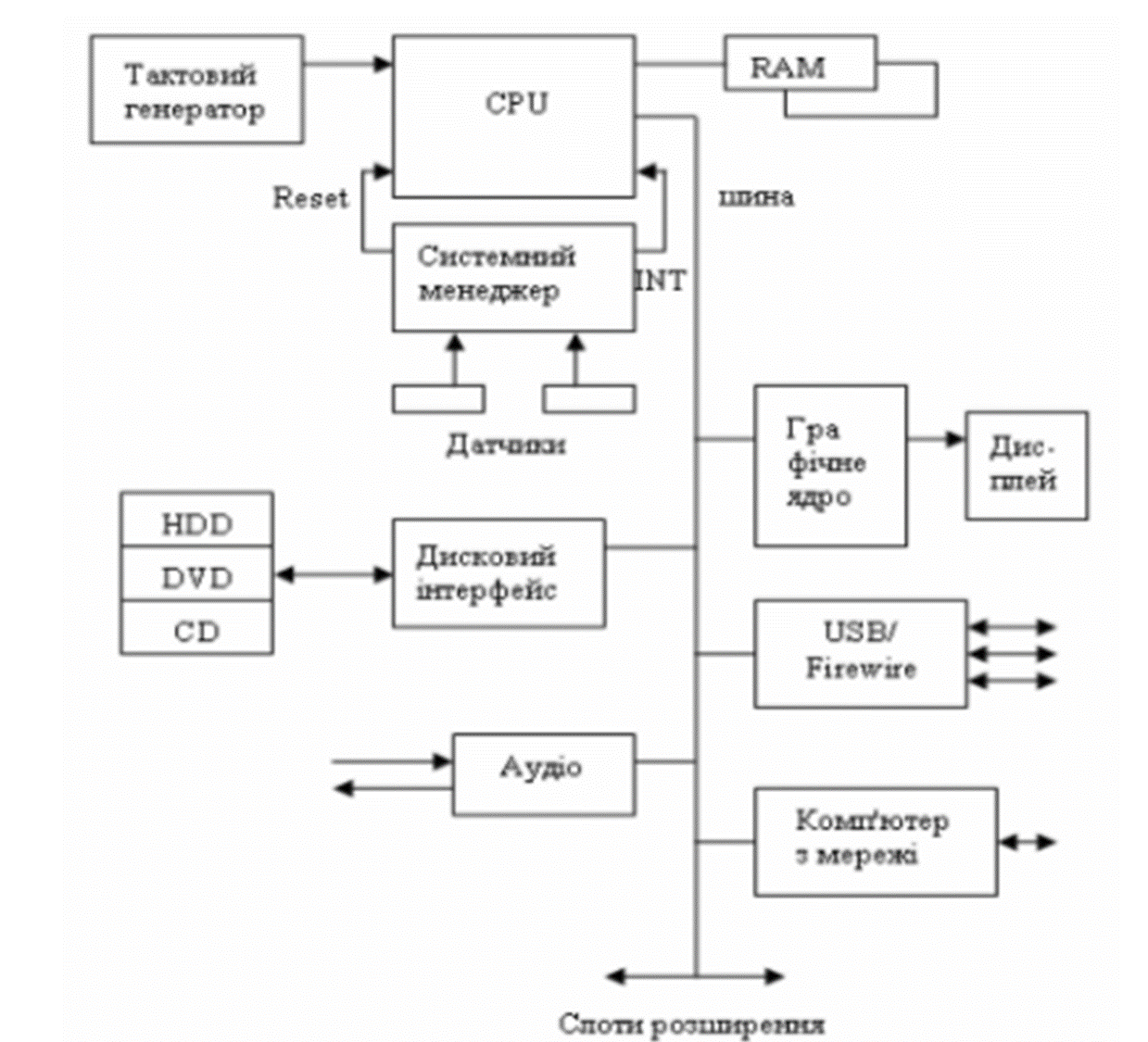

Архітектура вбудованих комп’ютерних систем. Схема комп'ютера загального призначення

4. Контрольні питання

Контрольні питання

- Якого роду інформація записується в УФ-ПЗП мікроконтроле- ра?

- Які параметри програмування УФ-ПЗП мікроконтролера, побудованого на основі технології п-МОН?

- Які параметри програмування УФ-ПЗП мікроконтролера, побудованого на основі технології к-МОН?

- Які засоби передбачені в МК з УФ-ПЗП для захисту від читання пам'яті програм ззовні?

- Яким чином здійснюється стирання вмісту УФ-ПЗП?

5. Пам’ять та регістри загального призначення ( на прикладі запам'ятовувального пристрою МК х51)

Пам’ять та регістри загального призначення ( на прикладі запам'ятовувального пристрою МК

х51)

Для спілкування із зовнішніми запам'ятовувальними пристроями в мікроконтролері є два 16-розрядних регістри:

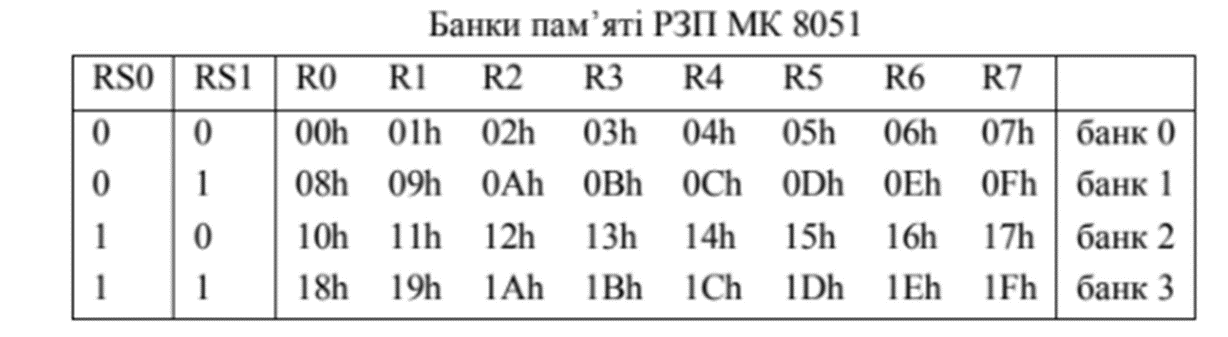

Початкові осередки оперативної пам'яті (32 байта) використовуються під

однобайтові регістри загального призначення (РЗП): R0, R1, R2,...R7.

Фізичні адреси регістрів загального призначення залежать від вмісту 3-го та 4-го розрядів регістра прапорців PSW (Processor Status Word)

Пам’ять та регістри загального призначення ( на прикладі запам'ятовувального пристрою МК х51)

Спеціальні функціональні регістри (SFR) являють собою комірки, пов'язані з особливими функціями мікроконтролера і його внутрішніх пристроїв.

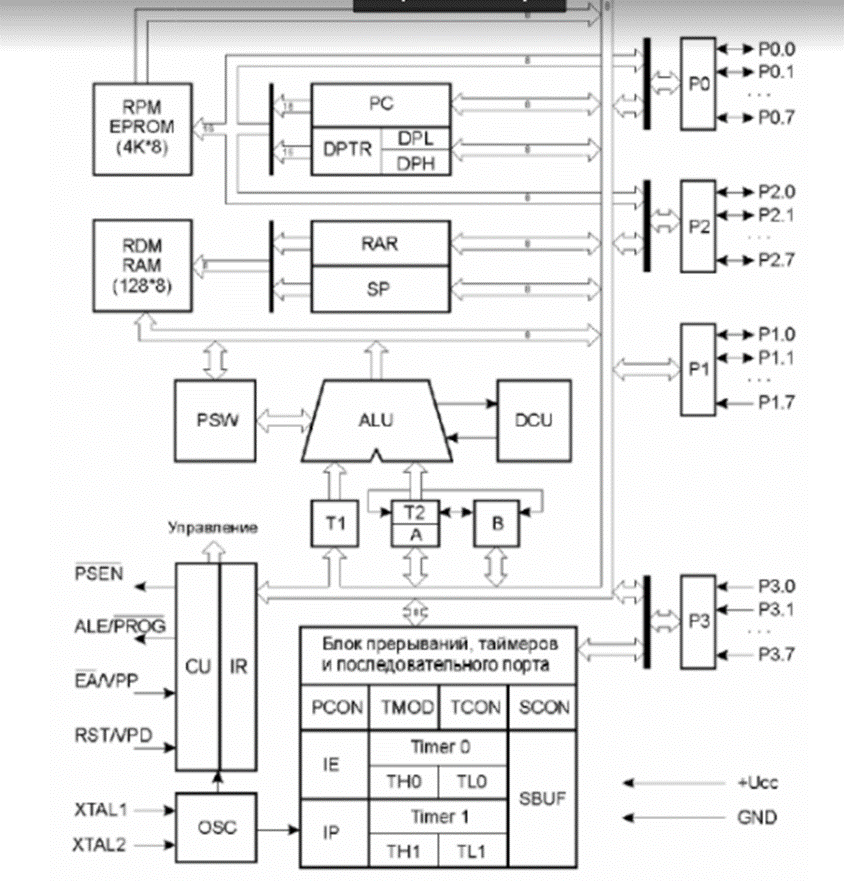

Структурна схема мікроконтролера 8051

Блоки

Лінії та сигнали:

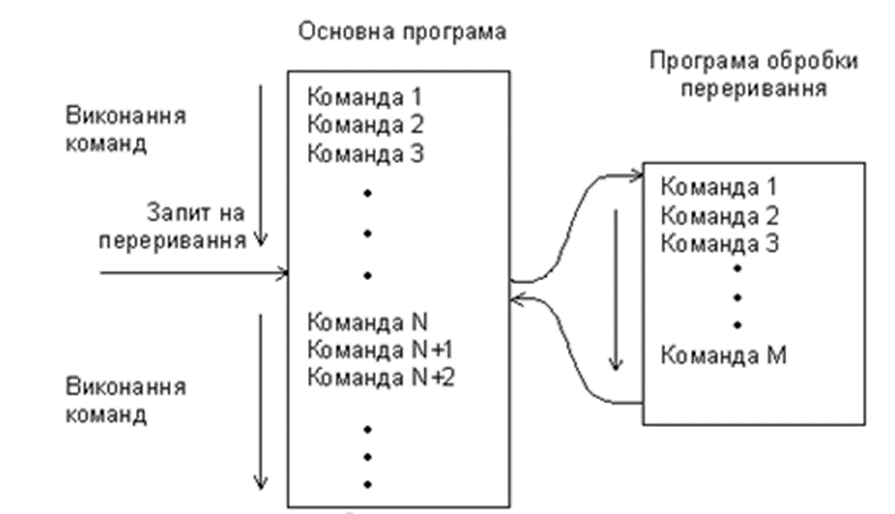

Для роботи мікроконтролера із зовнішніми об'єктами в реальному масштабі часу в його складі є система переривань. Для роботи із системою переривань використовуються:

6. Відладчики роботи МК

Відладчики роботи МК

Відладчики можна розділити на:

7. Цикл виконання команди ( на прикладі запам'ятовувального пристрою МК х51)

Цикл виконання команди ( на прикладі запам'ятовувального пристрою МК

х51)

Цикл виконання команди складається з таких кроків:

1. Читання коду з ПЗП за адресою з PC (з наступним інкрементуванням PC);

2. Читання операндів команди;

3. Виконання команди;

4. Збереження результатів (після цього PC вказує на наступну команду).

Цикл виконання різних команд займає від 1 до 10 тактів. Період

такту дорівнює 12 коливанням кварцового резонатора (при Чрез = 12

МГц період такту дорівнює 1 мкс).

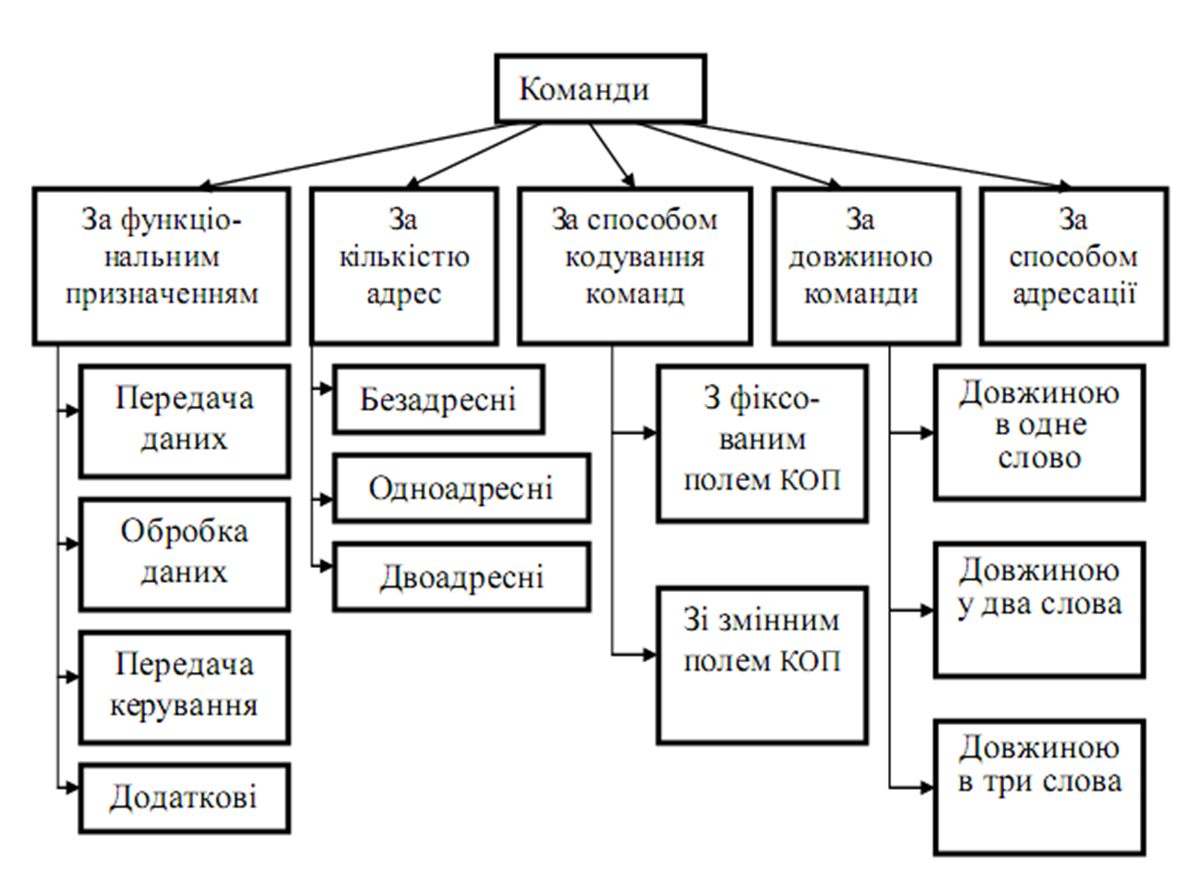

МП розроблена безліч способів звертання до пам'яті, називаних режимами адресації

Режим адресації пам'яті – це процедура або схема перетворення адресної інформації про операнда на його виконавчу адресу.

*код операції (КОп)

Усі способи адресації пам'яті можна поділити на:

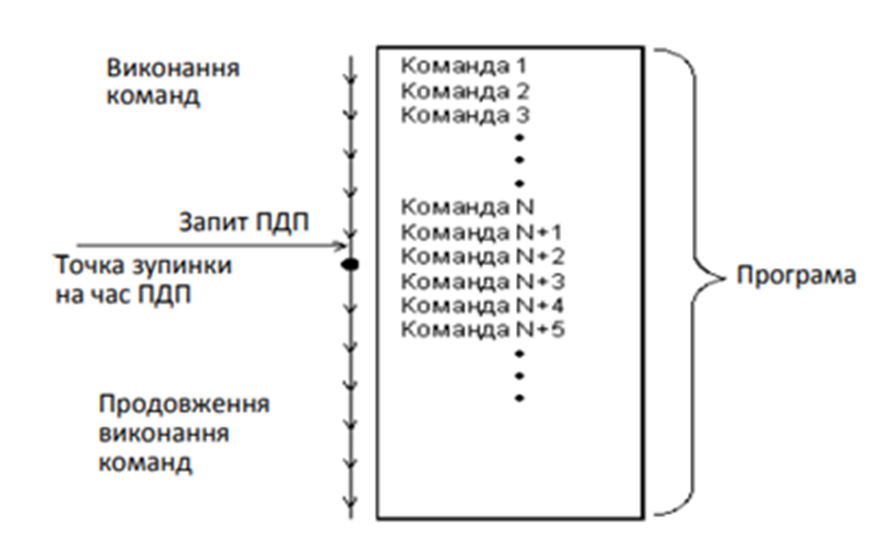

Операція ПДП зводиться до пересилання інформації з пристрою вводу/виводу в пам'ять або з пам'яті в пристрій вводу/виводу. Коли пересилання інформації буде завершено, процесор знову повертається до перерваної програми, продовжуючи її з того місця, де його перервали

Шрифти

Розмір шрифта

Колір тексту

Колір тла

Кернінг шрифтів

Видимість картинок

Інтервал між літерами

Висота рядка

Виділити посилання

Вирівнювання тексту

Ширина абзацу